REDHAWK Executable Device Pattern

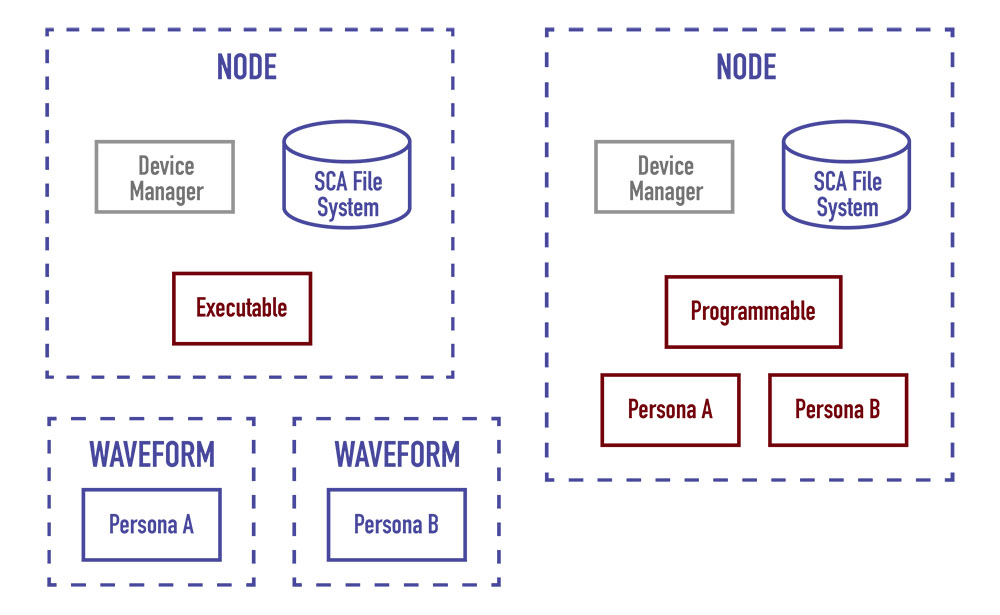

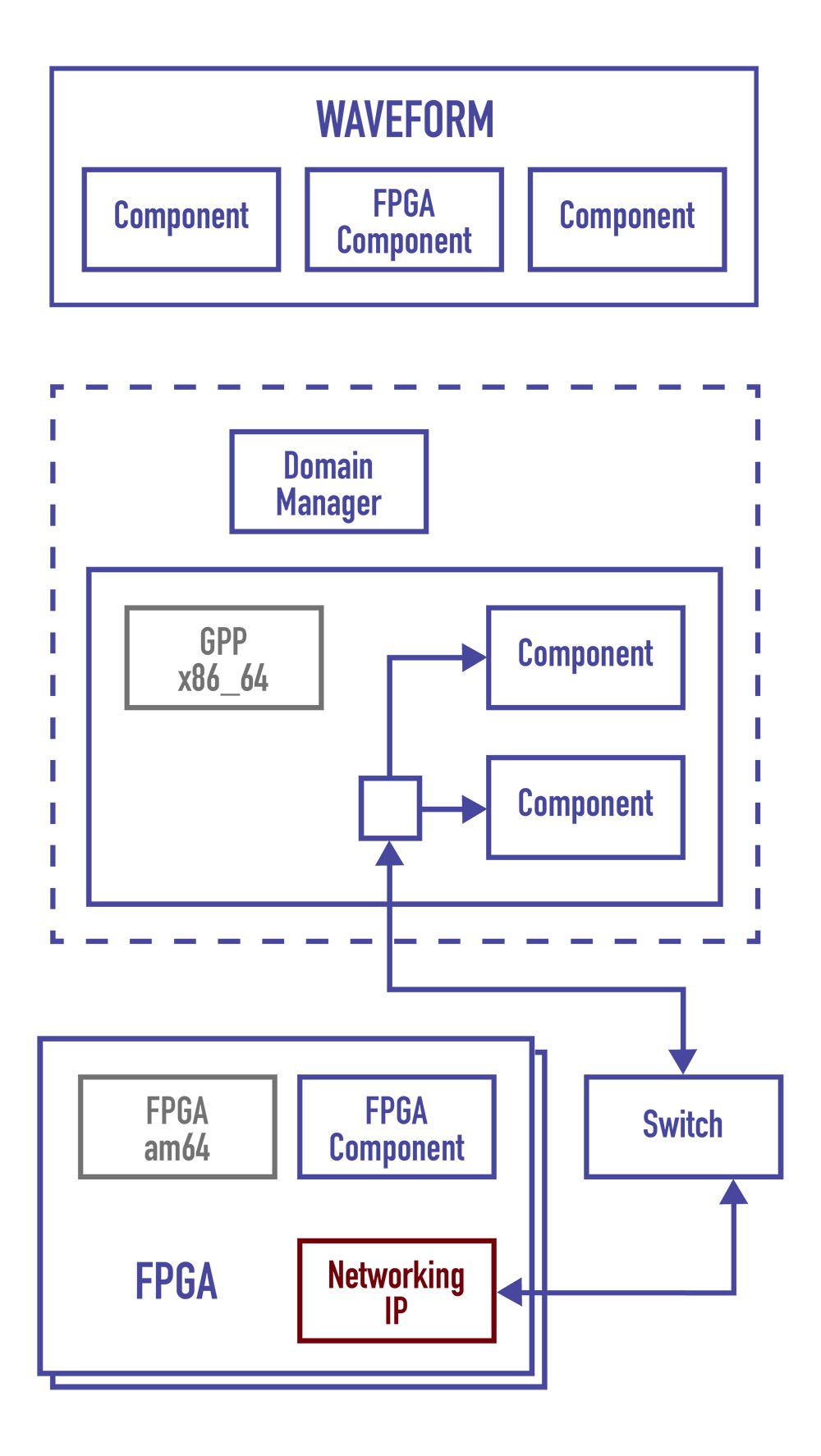

In the past Geon has used the Persona Device pattern to manage the deployment and control of FPGA IP within REDHAWK. But more recently the team has been using a much simpler pattern when integrating with FPGAs. This new pattern implements Customized exeutable devices to load FPGAs and REDHAWK components as the integration pattern. This allows for a more initiative execution enviroment in the REDHAWK Domain. A component is added to a waveform and the executable device loads the FPGA as a by-product of the component being launched. This implementation removes the step of manually launching a Programmable Device prior to launching the waveform as was previously required.

Geon developed a prototype using this pattern that was deployed on a system with multiple Intel Stratix10 development boards. The prototype took advantage of our open-source vrtgen tool to create a configurable VITA49 backplane for all of the connected processors to communicate. The backplane is automatically reconfigured to be connected differently based upon the connections that were specified in the waveform.

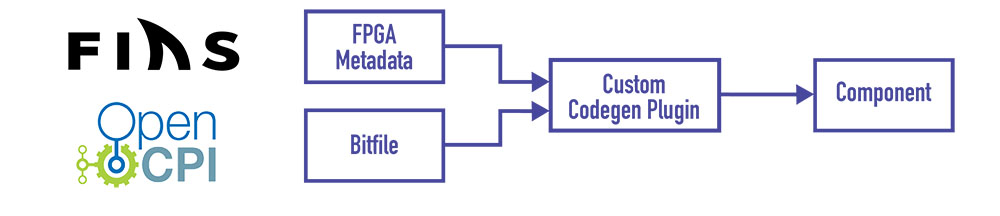

In order to accelerate the integration process of FPGA IP into REDHAWK, Geon also created a plugin to the REDHAWK code generator that creates the components with properties that are specified in a metadata file. These properties are intended to mirror any runtime configurable registers in FPGA fabric. Geon demonstrated this process with FPGA designs that were created with both OpenCPI and Geon’s open-source FINS tooling.

If you are interested to learn more about Geon’s work with FPGAs and REDHAWK please contact us.