Announcement

The Geon Technologies fork of OpenCPI and HiTech Global ZRF8 Board Support Package bring initial support of the Xilinx RF Data Converter to OpenCPI.

Usage

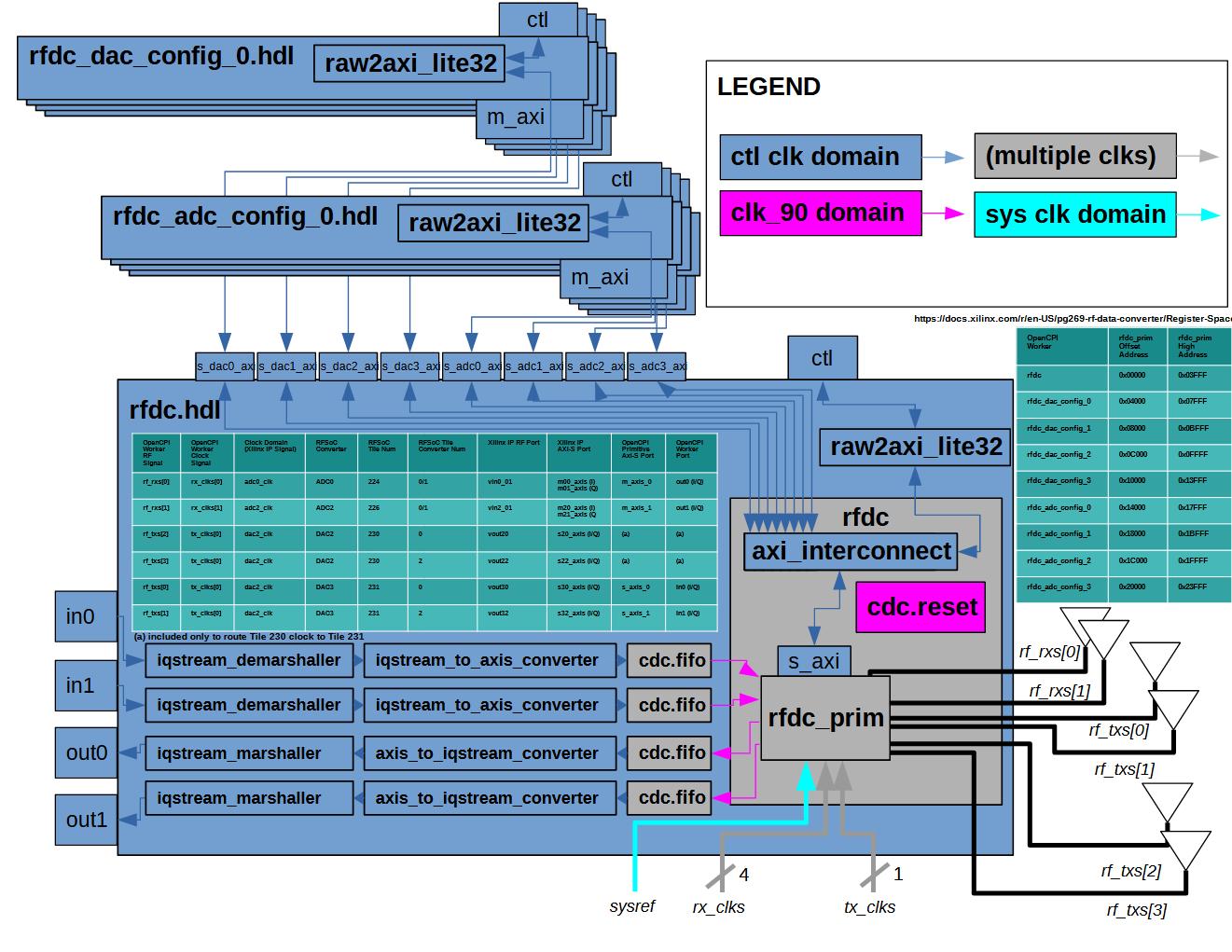

The rfdc prerequisite, rfdc HDL primitive, and rfdc.hdl, rfdc*hdl device workers comprise the OpenCPI RFDC FPGA support.

It is recommended to instance the device workers in a platform and its config, as the RFDC is a part of the FPGA platform itself (as opposed to an external device on an external card, which usually warrants instancing in an HDL assembly container). An example of this for the ZRF8 platform is here.

Assembly containers are constructed in the usual way, referring to any relevant platform configs.

It is recommended to include the Vivado IP-generated XCI file for the rfdc primitive in any assembly build so that proper constraints are applied and static timing analysis will include the RFDC internals. The Xilinx IP is referred via the XCI output product. Because OpenCPI does not natively support XCI inclusion, the following undocumented Make variable is used to force use of the XCI.

Assemblies are built in the usual way:

After the assembly builds, its timing analysis report can be visually inspected for timing closure and assessment of RFDC clock domains.

Test and Verification

Design Approach

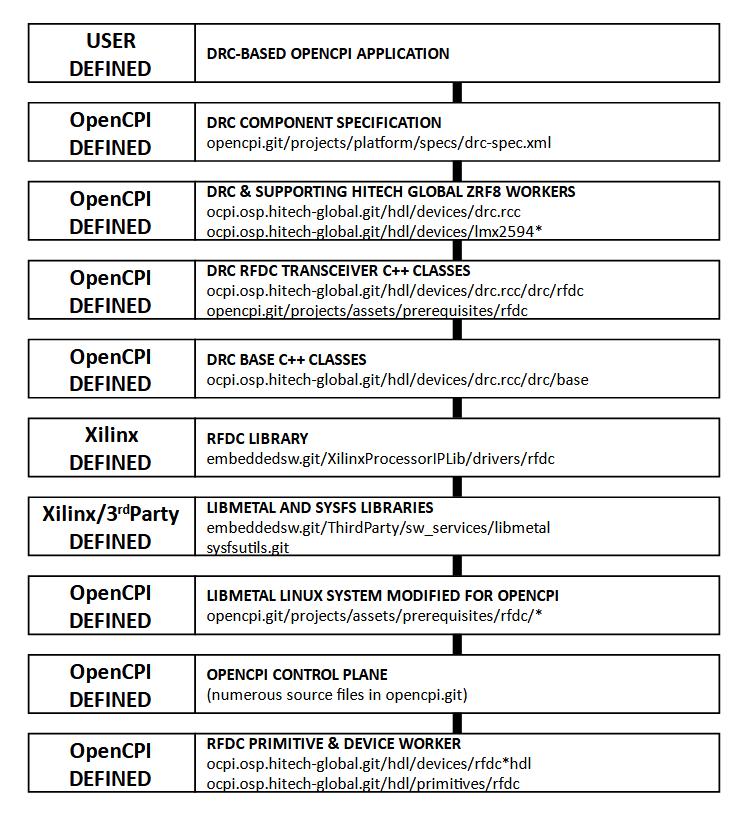

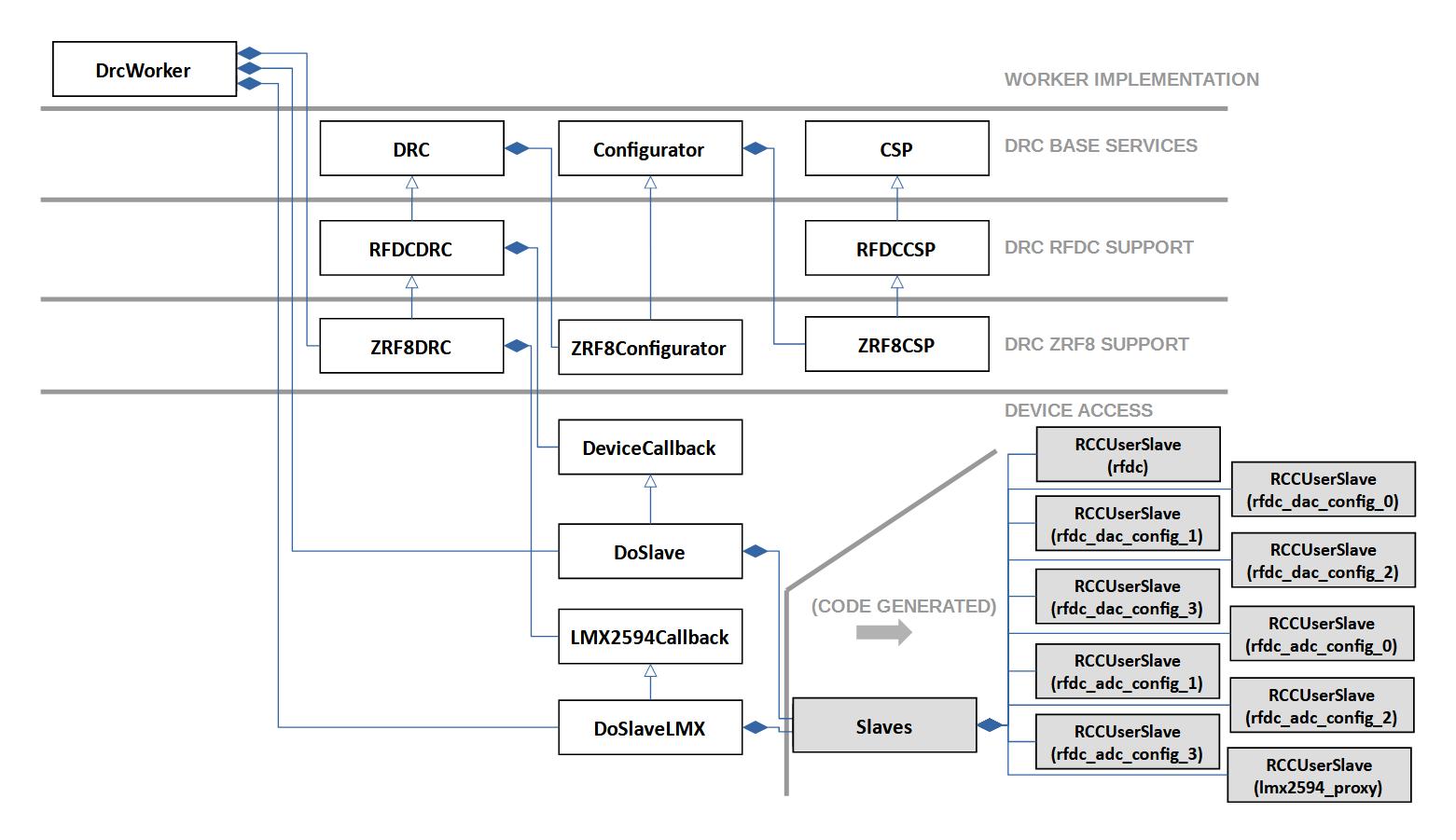

Xilinx provides FPGA IP and a software library which allow integration of the RFDC into custom designs. The OpenCPI RFDC support stack leverages these by “wrapping” them in OpenCPI workers that expose the standard OpenCPI interfaces for control (control plane API , DRC component specification) and data (Worker Stream Interfaces (WSI), iqstream protocol). Convience libraries exist simplifying the handling of DRC API and state machine (ref) as well as WSI data marshaling (ref).