Geon Technologies is well-known for leading the industry in software-defined radio (SDR) frameworks like REDHAWK SDR. However, Geon’s growing portfolio of exciting FPGA projects deserve the spotlight too! This post gives you a recap of some of the FPGA projects Geon (a Xilinx Alliance Program Member) has developed.

DSP Algorithms

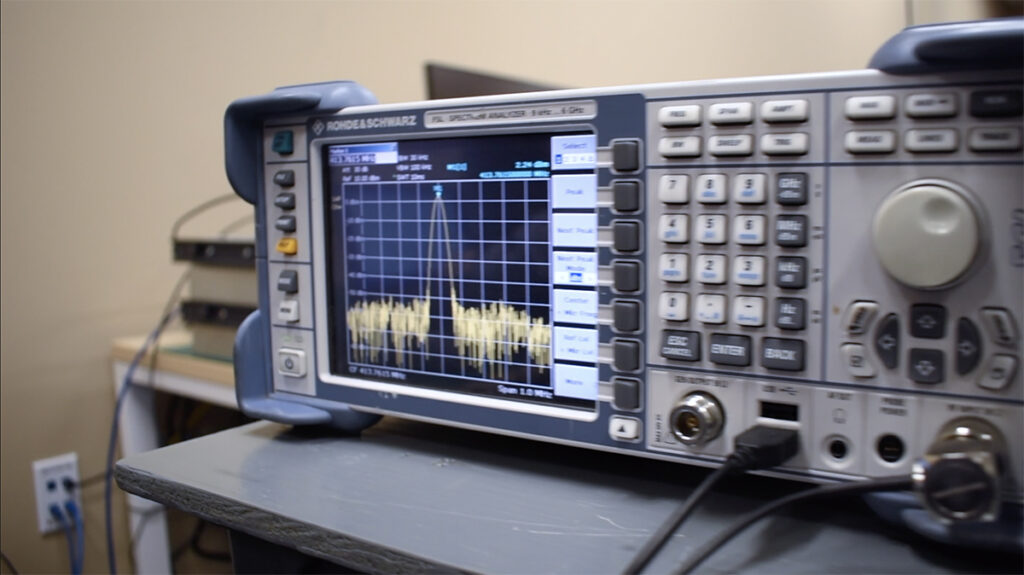

Energy Detector with the Ettus B205mini/Spectranetix MicroScan

Geon developed an energy detector FGPA for Electronic Warfare (EW) missions during dismounted operations. Despite the resource-constrained devices, the algorithm uses advanced techniques like noise-riding thresholds to handle dynamic spectral environments. This project was the first to be accelerated with the open-source FINS HDL code generator tool developed by Geon. The portability of a FINS Intellectual Property (IP) module was highlighted with a rapid rehost of the IP from the Ettus B205mini to the Spectranetix MicroScan.

Helo RADAR Spoofer with the Zedboard+FMCOMMS3

Utilizing Geon’s Zedboard+FMCOMMS3 platform, Geon designed and integrated an algorithm to spoof a helicopter’s RADAR return. The algorithm was developed and integrated in several weeks – an unheard of timeline for Programmable Logic projects. The customer’s requirement for a simple software control interface was easily met with the FINS C++ software library.

RADAR Simulation LFM Generator with the Picozed+FMCOMMS3

As part of building a RADAR simulation appliance, Geon developed a programmable Linear Frequency Modulation (LFM) generator with adjustable noise. The data from this LFM generator provided effects on the simulated RADAR return for testing large-scale antenna arrays. The FINS code generator tool was used heavily in this design to auto-generate software-controllable registers.

Frequency Estimator with the ZCU102

Geon’s modular firmware design best practices were on full display when the combination of reuse and FINS code generation compressed the development time of a frequency estimator module by more than a month. The functionality was demonstrated with a Xilinx ZCU102 development kit, and Geon’s standard model-driven approach validated the simulation with MATLAB code.

Passive RADAR Correlation Engine with the ZCU106+Epiq Sidekiq X4

To support a passive RADAR project, Geon developed a dual-channel correlation engine to detect signal returns. This project’s design challenges included generating correlations at high intervals of time slices and synchronization across IF channels.

Distributed TDOA Power Detector on the Picozed+FMCOMMS

As part of ongoing IR&D efforts, Geon designed a Time Difference of Arrival (TDOA) power detection FPGA with the Avnet Picozed and Analog Devices FMCOMMS3. The solution uses multiple spatially-distributed FPGA nodes to detect energy in the environment and report a precise detection time. The time within each distributed node is synchronized with the central TDOA server using the PTPv2 protocol.

Networking & Interfaces

VITA 49.0

A requirement for most contemporary SDR projects is data communication using the VITA 49.0 Radio Transport protocol. Geon developed IP cores to frame and deframe VITA 49.0 data and context packets on an FPGA. These cores were tested in hardware with 10G Ethernet on the Xilinx ZCU102 and with 100G Ethernet on the Intel Stratix 10 SX. The 10G Ethernet system on the ZCU102 also implemented the Modular Open Radio Frequency Architecture (MORA) standard. In simulation, these IP cores were validated using Geon’s in-house VITA 49.0 Python package. Stay tuned for more news on what Geon is doing with VITA 49.2!

100G Ethernet

To provide robust communications across a 100G Ethernet backbone, Geon designed a highly flexible FINS IP core to perform framing and deframing of Ethernet, IP, and UDP packets. The IP core can receive and transmit a build-time selectable number of channels, and it arbitrates transmit packets and filters receive packets to communicate on multiple channels. In addition to the basic UDP/IP framing and deframing, Geon developed code for common Network Layer and Link Layer protocols (ICMP IGMP, and ARP) for integration with switches and routers. Geon has tested 1, 2, and 4 channel variants with the Intel Stratix 10 SX. The 100G IP Core is compatible with Xilinx Vivado due to the platform-agnosticism provided by FINS; however, no Xilinx hardware integrations efforts are underway.

10G Ethernet

Geon developed a 10G Ethernet IP core for framing and deframing of Ethernet, IP, and UDP packets. The core processes both VITA 49.0 data and context packets and arbitrates between two channels. This IP core was tested by streaming data from the Analog Devices ADRV9371EBZ through the Xilinx ZCU102.

PTPv2 (IEEE 1588-2008)

Geon implemented Precision Time Protocol v2 (PTPv2) on the Zynq-7000 within the Programmable Logic (PL) fabric to support time synchronization between multiple remote clocks. This functionality is normally unavailable with the Zynq-7000 Processing System (PS) due to a bug in the chipset. Hardware testing demonstrated that PTPv2 synchronization could be maintained within 1us!

PCIe with HiTech Global HTG-ZRF8

To characterize the high-speed data transfer from FPGA to Software, Geon implemented the benchmarking described in Xilinx’s Answer Record (AR7153) for the HiTech Global HTG-ZRF8. Both Kernel and DPDK module tests were built and executed.

Xilinx RF Analyzer with HiTech Global HTG-ZRF8

The RF Analyzer is a utility provided for use with the RF Data Converters in Zynq UltraScale+ RFSoC. Geon created a design that allows the HTG-ZRF8 to communicate with the Xilinx RF Analyzer Tool for rapid profiling of the A/D converters.

Board Support Packages

Avnet Zedboard + Analog Devices FMCOMMS3

A common interest of SDR prototyping efforts is the quick integration of Digital Signal Processing (DSP) FPGA capabilities with the low-cost Zedboard and Analog Devices FMCOMMS3 combination. Along with the embedded operating system which integrated REDHAWK SDR, Geon developed a pattern and platform codebase for easy integration of DSP capabilities.

Avnet Picozed + Analog Devices FMCOMMS3

Geon created Programmable Logic (PL) code for an Avnet Picozed to interface with the Analog Devices FMCOMMS3. This combination enables the rapid prototyping of the FMCOMMS3 with the more robust interfaces of the Picozed FMC Carrier Card V2.

Geon developed Board Support Packages in the heterogeneous computing framework OpenCPI for the Avnet Picozed. These inexpensive Zynq-7000 based platforms can be used for learning OpenCPI or rapid prototyping with OpenCPI’s library of components.

Xilinx ZCU102/ZCU111

Geon leveraged years of experience with OpenCPI to develop Board Support Packages for the Xilinx ZCU102 and ZCU111. Traditionally an effort requiring a year to complete, Geon developed the board support packages in under two months. These platforms paved the way for the development of an OpenCPI Platform for any Xilinx Ultrascale+ architecture.

In addition to the work with OpenCPI, Geon has integrated networking and DSP algorithm code on the Xilinx ZCU102 and has done some preliminary testing with 100G Ethernet on the Xilinx ZCU111.

Xilinx ZCU106 + Epiq Sidekiq x4

Geon was the first to integrate the Epiq Sidekiq X4 with a Xilinx Zynq Ultrascale+, the Xilinx ZCU106. The effort required a deep knowledge of interface design with JESD204B. The pairing of the ZCU106 with the Sidekiq x4 provides a potent quad-channel receiver in a smaller form factor than most other Ultrascale+ development kits.

Intel Stratix 10 SX

To serve as the foundation for building bitstreams on a large-scale project, Geon created a reusable and maintainable platform for the Intel Stratix 10 SX. Geon started with Intel’s Golden Hardware Reference Design (GHRD) and added 100G Ethernet and VITA 49.0 support. Geon used and integrated the platform with Intel Platform Designer, allowing the use of graphical tools for system and application design entry. Geon integrated this platform with an embedded operating system built with Yocto, and also demonstrated partial reconfiguration and DMA on the platform.

Geon also developed an OpenCPI Board Support Package for the Intel Stratix 10 SX. This effort required significant modifications to the framework to support the latest versions of Intel Quartus Prime Pro. These upgrades to OpenCPI permit faster development of Intel devices in the future.

Get in Touch

Contact us for ways our FPGA team can bring solutions like these to your project, or join us to be a part of our growing team!